ready-to-use solution for different applications to offload processing of high-speed network traffic into FPGA accelerator card. It completely remove the risk, uncertainty, and time of FPGA firmware development. Customer creates only software without the need for FPGA know-how and HW development team. Solution provides single standardized API following DPDK standard. It supports packet transfers using our Ultra-Fast FPGA DMA engine with open-source drivers, dynamic software-defined RTE Flow filtering and offload with multiple rule tables, static configuration of traffic processing, dynamic traffic flow management and many more.

Main features and benefits of solution

Just don’t care about FPGA design!

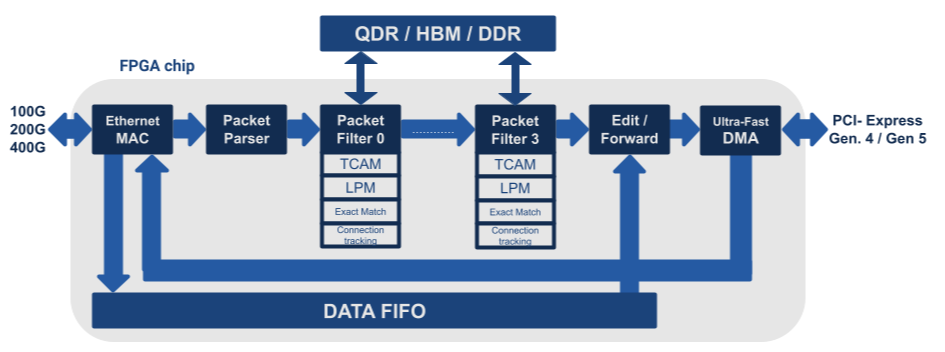

Processing pipeline

Provided as a “bitstream” for given FPGA accelerator card.

See some other technical details of FPGA accelerated DPDK SmartNIC solution on XpressSX AGI-FH400G.